-

TERMINALS

- TERMINALS

-

WIRELESS MODULES

- WIRELESS MODULES

-

DEVELOPMENT BOARDS & KITS

- DEVELOPMENT BOARDS & KITS

-

RF and Wireless

- RF and Wireless

-

SINGLE BOARD COMPUTER

- SINGLE BOARD COMPUTER

-

BREAKOUT BOARDS

- BREAKOUT BOARDS

-

LED

- LED

-

LCD & DISPLAYS

- LCD & DISPLAYS

-

TEST AND MEASUREMENT

- TEST AND MEASUREMENT

-

DEVELOPMENT BOARDS AND IC's

- DEVELOPMENT BOARDS AND IC's

-

CABLES/WIRES/FANS

- CABLES/WIRES/FANS

-

EMBEDDED COMPUTERS

- EMBEDDED COMPUTERS

-

INDUSTRAL AUTOMATION AND CONTROL

- INDUSTRAL AUTOMATION AND CONTROL

-

COMPUTER EQUIPMENT

- COMPUTER EQUIPMENT

-

CONNECTORS & INTERCONNECTS

- CONNECTORS & INTERCONNECTS

-

MOTORS/DRIVERS/ACTUATORS/MODULES

- MOTORS/DRIVERS/ACTUATORS/MODULES

-

MAKER/DIY EDUCATIONAL

- MAKER/DIY EDUCATIONAL

-

BASIC COMPONENTS

- BASIC COMPONENTS

-

TOOLS & ACCESSORIES

- TOOLS & ACCESSORIES

-

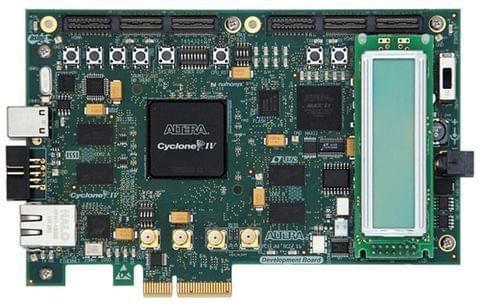

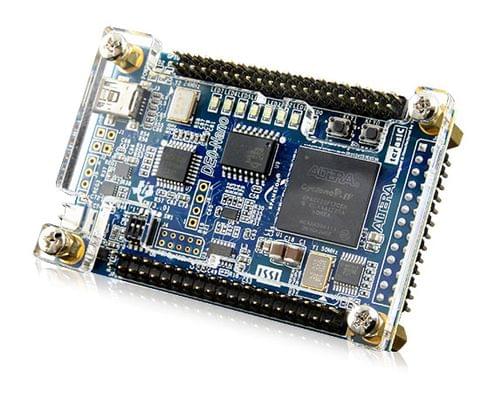

FPGA HARDWARE

- FPGA HARDWARE

-

ARTILA

- ARTILA

-

POWER SUPPLIES

- POWER SUPPLIES

-

ROBOTICS & AUTOMATION

- ROBOTICS & AUTOMATION

-

TRANSDUCERS

- TRANSDUCERS

-

MEMORY CARDS & MODULES

- MEMORY CARDS & MODULES

-

SOFTWARE

- SOFTWARE

Description

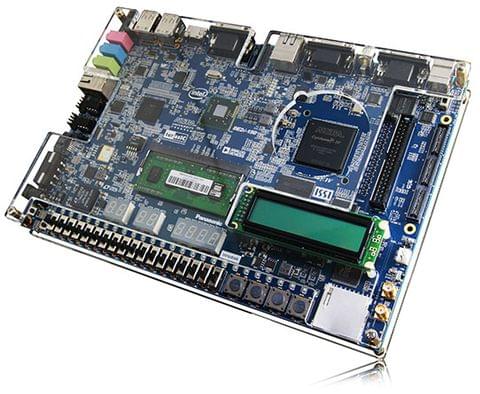

The VEEK-MT2S Development Kit is a comprehensive embedded design environment with everything developers need to create processing-based systems. The VEEK-MT2S delivers an integrated platform including hardware, design tools, and reference designs for developing embedded software and hardware platforms in a wide range of applications. The fully integrated kit allows developers to rapidly customize their processor and IP to best suit their specific application. The VEEK-MT2S features a DE10-Standard development board targeting Intel Cyclone® V SX SoC FPGA, as well as a capacitive LCD multimedia color touch panel which supports 5-point multi-touch and gestures.

The all-in-one embedded solution offered on the VEEK-MT2S, in combination with LCD touch panel and digital image module, provides developers the ideal platform for multimedia applications with unparallel processing performance. Developers can benefit from the use of FPGA-based embedded processing system utilizing mitigating design risk and obsolescence, design reuse, reducing bill of material (BOM) costs by integrating powerful graphics engines within the FPGA.

Please refer to the VEEK-MT2S Control Panel for SoC reference design in Linux touch-screen display.

Cyclone V SX SoC—5CSXFC6D6F31C6N

- Dual-core ARM Cortex-A9 (HPS)

- 110K programmable logic elements

- 5,761 Kbits embedded memory

- 6 fractional PLLs

- 2 hard memory controllers

- Serial configuration device – EPCS128 for the FPGA

- On-board USB Blaster II (normal type B USB connector)

- 64MB (32Mx16) SDRAM for the FPGA

- 1GB (2x256MBx16) DDR3 SDRAM for the HPS

- microSD card socket for the HPS

- Two USB 2.0 Host Ports (ULPI interface with USB type A connector) on HPS

- UART to USB (USB Mini B connector)

- 10/100/1000 Ethernet

- PS/2 mouse/keyboard

- IR emitter/receiver

- I2C multiplexer

- One HSMC expansion header (used for MTLC2)

- One 40-pin expansion header

- One 10-pin ADC input header

- One LTC connector (one Serial Peripheral Interface (SPI) master ,one I2C bus, and one GPIO interface)

- 24-bit VGA DAC

- 128x64 dots LCD Module with Backlight on HPS

- 24-bit CODEC, Line-in, line-out, and microphone-in jack

- TV decoder (NTSC/PAL/SECAM) and Video-in connector

TT-TS-029

- Home

- FPGA HARDWARE

- INTEL FPGA

- VEEK-MT2S

VEEK-MT2S

SIZE GUIDE

- Shipping in 10-12 Working days

- http://cdn.storehippo.com/s/59c9e4669bd3e7c70c5f5e6c/ms.products/5b924cd86cd2416066e62e7a/images/5b924cd86cd2416066e62e7b/5b924cb114c36b60658c8644/5b924cb114c36b60658c8644.jpg

Description of product

Description

The VEEK-MT2S Development Kit is a comprehensive embedded design environment with everything developers need to create processing-based systems. The VEEK-MT2S delivers an integrated platform including hardware, design tools, and reference designs for developing embedded software and hardware platforms in a wide range of applications. The fully integrated kit allows developers to rapidly customize their processor and IP to best suit their specific application. The VEEK-MT2S features a DE10-Standard development board targeting Intel Cyclone® V SX SoC FPGA, as well as a capacitive LCD multimedia color touch panel which supports 5-point multi-touch and gestures.

The all-in-one embedded solution offered on the VEEK-MT2S, in combination with LCD touch panel and digital image module, provides developers the ideal platform for multimedia applications with unparallel processing performance. Developers can benefit from the use of FPGA-based embedded processing system utilizing mitigating design risk and obsolescence, design reuse, reducing bill of material (BOM) costs by integrating powerful graphics engines within the FPGA.

Please refer to the VEEK-MT2S Control Panel for SoC reference design in Linux touch-screen display.

Cyclone V SX SoC—5CSXFC6D6F31C6N

- Dual-core ARM Cortex-A9 (HPS)

- 110K programmable logic elements

- 5,761 Kbits embedded memory

- 6 fractional PLLs

- 2 hard memory controllers

- Serial configuration device – EPCS128 for the FPGA

- On-board USB Blaster II (normal type B USB connector)

- 64MB (32Mx16) SDRAM for the FPGA

- 1GB (2x256MBx16) DDR3 SDRAM for the HPS

- microSD card socket for the HPS

- Two USB 2.0 Host Ports (ULPI interface with USB type A connector) on HPS

- UART to USB (USB Mini B connector)

- 10/100/1000 Ethernet

- PS/2 mouse/keyboard

- IR emitter/receiver

- I2C multiplexer

- One HSMC expansion header (used for MTLC2)

- One 40-pin expansion header

- One 10-pin ADC input header

- One LTC connector (one Serial Peripheral Interface (SPI) master ,one I2C bus, and one GPIO interface)

- 24-bit VGA DAC

- 128x64 dots LCD Module with Backlight on HPS

- 24-bit CODEC, Line-in, line-out, and microphone-in jack

- TV decoder (NTSC/PAL/SECAM) and Video-in connector

NEWSLETTER

Subscribe to get Email Updates!

Thanks for subscribe.

Your response has been recorded.

INFORMATION

ACCOUNT

ADDRESS

Tenet Technetronics# 2514/U, 7th 'A' Main Road, Opp. to BBMP Swimming Pool, Hampinagar, Vijayanagar 2nd Stage.

Bangalore

Karnataka - 560104

IN

Tenet Technetronics focuses on “Simplifying Technology for Life” and has been striving to deliver the same from the day of its inception since 2007. Founded by young set of graduates with guidance from ardent professionals and academicians the company focuses on delivering high quality products to its customers at the right cost considering the support and lifelong engagement with customers. “We don’t believe in a sell and forget model “and concentrate and building relationships with customers that accelerates, enhances as well as provides excellence in their next exciting project.