- TERMINALS

- TERMINALS

- WIRELESS MODULES

- WIRELESS MODULES

- DEVELOPMENT BOARDS & KITS

- DEVELOPMENT BOARDS & KITS

- RF and Wireless

- RF and Wireless

- SINGLE BOARD COMPUTER

- SINGLE BOARD COMPUTER

- BREAKOUT BOARDS

- BREAKOUT BOARDS

- LED

- LED

- TEST AND MEASUREMENT

- TEST AND MEASUREMENT

- DEVELOPMENT BOARDS AND IC's

- DEVELOPMENT BOARDS AND IC's

- CABLES/WIRES/FANS

- CABLES/WIRES/FANS

- EMBEDDED COMPUTERS

- EMBEDDED COMPUTERS

- INDUSTRAL AUTOMATION AND CONTROL

- INDUSTRAL AUTOMATION AND CONTROL

- COMPUTER EQUIPMENT

- COMPUTER EQUIPMENT

- CONNECTORS & INTERCONNECTS

- CONNECTORS & INTERCONNECTS

- MOTORS/DRIVERS/ACTUATORS/MODULES

- MOTORS/DRIVERS/ACTUATORS/MODULES

- MAKER/DIY EDUCATIONAL

- MAKER/DIY EDUCATIONAL

- BASIC COMPONENTS

- BASIC COMPONENTS

- TOOLS & ACCESSORIES

- TOOLS & ACCESSORIES

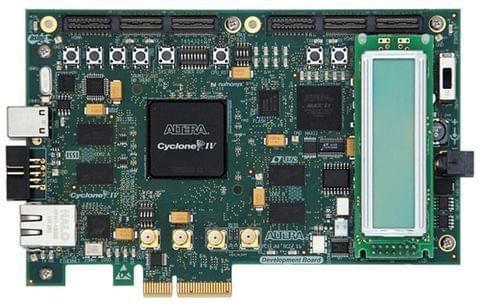

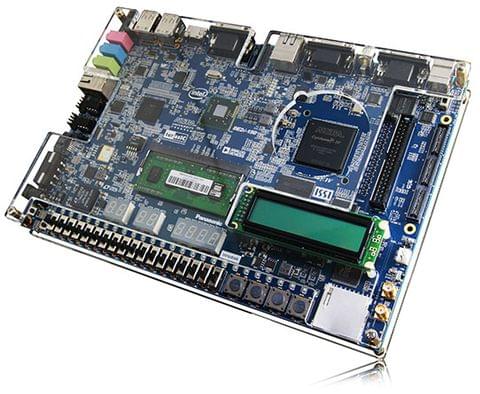

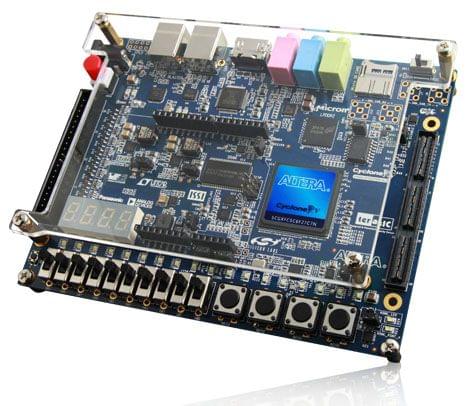

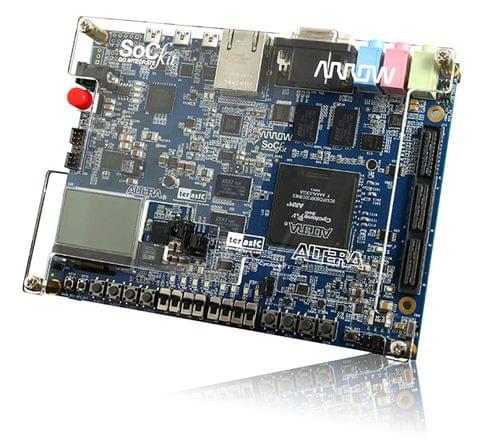

- FPGA HARDWARE

- FPGA HARDWARE

- POWER SUPPLIES

- POWER SUPPLIES

- ROBOTICS & AUTOMATION

- ROBOTICS & AUTOMATION

- TRANSDUCERS

- TRANSDUCERS

- MEMORY CARDS & MODULES

- MEMORY CARDS & MODULES

- SOFTWARE

- SOFTWARE

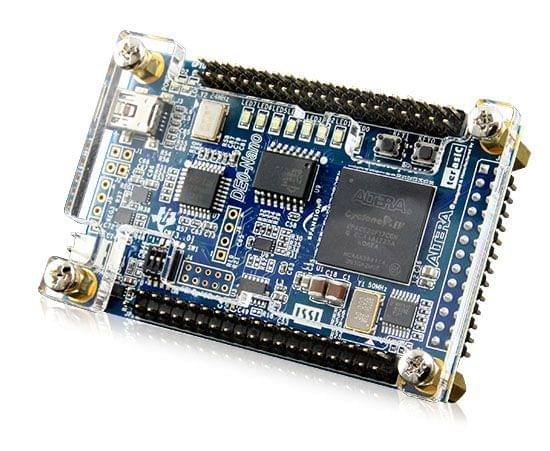

Description

The DE0-Nano board introduces a compact-sized FPGA development platform suited for prototyping circuit designs such as robots and "portable" projects. The board is designed to be used in the simplest possible implementation targeting the Cyclone IV device up to 22,320 LEs.

The DE0-Nano has a collection of interfaces including two external GPIO headers to extend designs beyond the DE0-Nano board, on-board memory devices including SDRAM and EEPROM for larger data storage and frame buffering, as well as general user peripheral with LEDs and push-buttons.

The advantages of the DE0-Nano board include its size and weight, as well as its ability to be reconfigured without carrying superfluous hardware, setting itself apart from other general purpose development boards. In addition, for mobile designs where portable power is crucial, the DE0-Nano provides designers with three power scheme options including a USB mini-AB port, 2-pin external power header and two DC 5V pins

Cyclone® IV EP4CE22F17C6N FPGA

- 22,320 Logic elements (LEs)

- 594 Embedded memory (Kbits)

- 66 Embedded 18 x 18 multipliers

- 4 General-purpose PLLs

- 153 Maximum FPGA I/O pins

Configuration Status and Set-Up Elements

- On-board USB-Blaster circuit for programming

- FPGA Serial Configuration Device (EPCS)

Expansion Header

- Two 40-pin Headers (GPIOs) provides 72 3.3V I/O pins

- Two 5V power pins, two 3.3V power pins and four ground pins

- One 26-pin header provides 16 3.3V digital I/O pins and 8 analog input pins to connect to analog sensors, etc

Memory Devices

- 32MB SDRAM

- 2Kb I2C EEPROM

General User Input/Output

- 8 green LEDs

- 2 debounced push-buttons

- 4 dip switches

G-Sensor

- ADI ADXL345, 3-axis accelerometer with high resolution (13-bit)

A/D Converter

- NS ADC128S022, 8-Channel, 12-bit A/D Converter

- 50 ksps to 200 ksps

Clock System

- On-board 50MHz clock oscillator

Power Supply

- USB Type mini-AB port (5V)

- Two DC 5V pins of the GPIO headers (5V)

- 2-pin external power header (3.6-5.7V)

Connectivity

![]() Connect D5M

Connect D5M

TT-TS-043

- Connect with 5-megapixel CMOS Sensor (D5M)

- Home

- FPGA HARDWARE

- INTEL FPGA

- DE0-Nano Development and Education Board

DE0-Nano Development and Education Board

SIZE GUIDE

- Shipping in 10-12 Working days

- http://cdn.storehippo.com/s/59c9e4669bd3e7c70c5f5e6c/ms.products/5b939b94b7167eb27e67e202/images/5b939b94b7167eb27e67e203/5b939b54ac9e63b27856c50a/5b939b54ac9e63b27856c50a.jpg

Description of product

Description

The DE0-Nano board introduces a compact-sized FPGA development platform suited for prototyping circuit designs such as robots and "portable" projects. The board is designed to be used in the simplest possible implementation targeting the Cyclone IV device up to 22,320 LEs.

The DE0-Nano has a collection of interfaces including two external GPIO headers to extend designs beyond the DE0-Nano board, on-board memory devices including SDRAM and EEPROM for larger data storage and frame buffering, as well as general user peripheral with LEDs and push-buttons.

The advantages of the DE0-Nano board include its size and weight, as well as its ability to be reconfigured without carrying superfluous hardware, setting itself apart from other general purpose development boards. In addition, for mobile designs where portable power is crucial, the DE0-Nano provides designers with three power scheme options including a USB mini-AB port, 2-pin external power header and two DC 5V pins

Cyclone® IV EP4CE22F17C6N FPGA

- 22,320 Logic elements (LEs)

- 594 Embedded memory (Kbits)

- 66 Embedded 18 x 18 multipliers

- 4 General-purpose PLLs

- 153 Maximum FPGA I/O pins

Configuration Status and Set-Up Elements

- On-board USB-Blaster circuit for programming

- FPGA Serial Configuration Device (EPCS)

Expansion Header

- Two 40-pin Headers (GPIOs) provides 72 3.3V I/O pins

- Two 5V power pins, two 3.3V power pins and four ground pins

- One 26-pin header provides 16 3.3V digital I/O pins and 8 analog input pins to connect to analog sensors, etc

Memory Devices

- 32MB SDRAM

- 2Kb I2C EEPROM

General User Input/Output

- 8 green LEDs

- 2 debounced push-buttons

- 4 dip switches

G-Sensor

- ADI ADXL345, 3-axis accelerometer with high resolution (13-bit)

A/D Converter

- NS ADC128S022, 8-Channel, 12-bit A/D Converter

- 50 ksps to 200 ksps

Clock System

- On-board 50MHz clock oscillator

Power Supply

- USB Type mini-AB port (5V)

- Two DC 5V pins of the GPIO headers (5V)

- 2-pin external power header (3.6-5.7V)

Connectivity

![]() Connect D5M

Connect D5M

- Connect with 5-megapixel CMOS Sensor (D5M)

NEWSLETTER

Subscribe to get Email Updates!

Thanks for subscribe.

Your response has been recorded.

INFORMATION

ACCOUNT

ADDRESS

Tenet Technetronics# 2514/U, 7th 'A' Main Road, Opp. to BBMP Swimming Pool, Hampinagar, Vijayanagar 2nd Stage.

Bangalore

Karnataka - 560104

IN

Tenet Technetronics focuses on “Simplifying Technology for Life” and has been striving to deliver the same from the day of its inception since 2007. Founded by young set of graduates with guidance from ardent professionals and academicians the company focuses on delivering high quality products to its customers at the right cost considering the support and lifelong engagement with customers. “We don’t believe in a sell and forget model “and concentrate and building relationships with customers that accelerates, enhances as well as provides excellence in their next exciting project.