- TERMINALS

- TERMINALS

- WIRELESS MODULES

- WIRELESS MODULES

- DEVELOPMENT BOARDS & KITS

- DEVELOPMENT BOARDS & KITS

- RF and Wireless

- RF and Wireless

- SINGLE BOARD COMPUTER

- SINGLE BOARD COMPUTER

- BREAKOUT BOARDS

- BREAKOUT BOARDS

- LED

- LED

- TEST AND MEASUREMENT

- TEST AND MEASUREMENT

- DEVELOPMENT BOARDS AND IC's

- DEVELOPMENT BOARDS AND IC's

- CABLES/WIRES/FANS

- CABLES/WIRES/FANS

- EMBEDDED COMPUTERS

- EMBEDDED COMPUTERS

- INDUSTRAL AUTOMATION AND CONTROL

- INDUSTRAL AUTOMATION AND CONTROL

- COMPUTER EQUIPMENT

- COMPUTER EQUIPMENT

- CONNECTORS & INTERCONNECTS

- CONNECTORS & INTERCONNECTS

- MOTORS/DRIVERS/ACTUATORS/MODULES

- MOTORS/DRIVERS/ACTUATORS/MODULES

- MAKER/DIY EDUCATIONAL

- MAKER/DIY EDUCATIONAL

- BASIC COMPONENTS

- BASIC COMPONENTS

- TOOLS & ACCESSORIES

- TOOLS & ACCESSORIES

- FPGA HARDWARE

- FPGA HARDWARE

- POWER SUPPLIES

- POWER SUPPLIES

- ROBOTICS & AUTOMATION

- ROBOTICS & AUTOMATION

- TRANSDUCERS

- TRANSDUCERS

- MEMORY CARDS & MODULES

- MEMORY CARDS & MODULES

- SOFTWARE

- SOFTWARE

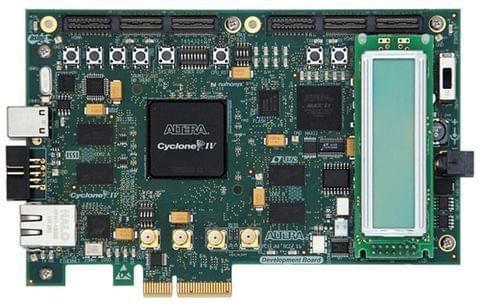

Description

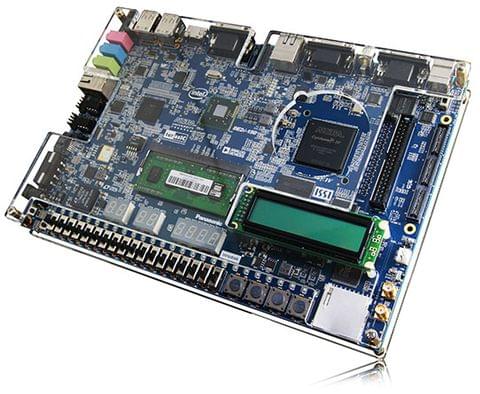

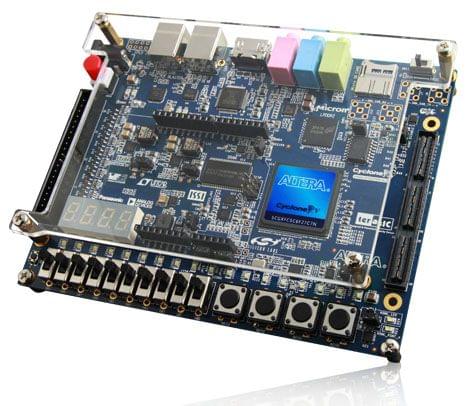

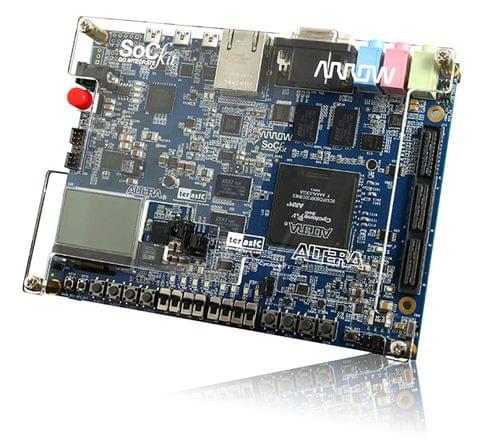

The DE0 Development and Education board is designed in a compact size with all the essential tools for novice users to gain knowledge in areas of digital logic, computer organization and FPGAs. It is equipped with Altera Cyclone III 3C16 FPGA device, which offers 15,408 LEDs. The board provides 346 user I/O pins, and is loaded with a rich set of features that makes it suitable to be used for advanced university and college courses, as well as the development of sophisticated digital systems. The DE0 combines the Altera low-power, low-cost, and high performance Cyclone III FPGA to control the various features of the DE0 Board. The DE0 Development Board includes software, reference designs, and accessories required to ensure the user simple access in evaluating their DE0 Board.

- FPGA

- Cyclone III 3C16 FPGA

- 15,408 LEs

- 56 M9K Embedded Memory Blocks

- 504K total RAM bits

- 56 embedded multipliers

- 4 PLLs

- 346 user I/O pins

- FineLine BGA 484-pin package

- Cyclone III 3C16 FPGA

- Memory

- SDRAM

- One 8-Mbyte Single Data Rate Synchronous Dynamic RAM memory chip

- Flash memory

- 4-Mbyte NOR Flash memory

- Support Byte (8-bits)/Word (16-bits) mode

- SD card socket

- Provides both SPI and SD 1-bit mode SD Card access

- SDRAM

- Interface

- Built-in USB Blaster circuit

- On-board USB Blaster for programming

- Using the Altera EPM240 CPLD

- Altera Serial Configuration device

- Altera EPCS4 serial EEPROM chip

- Pushbutton switches

- 3 pushbutton switches

- Slide switches

- 10 Slide switches

- General User Interfaces

- 10 Green color LEDs

- 4 seven-segment displays

- 16x2 LCD Interface (Not include LCD module)

- Clock inputs

- 50-MHz oscillator

- VGA output

- Uses a 4-bit resistor-network DAC

- With 15-pin high-density D-sub connector

- Supports up to 1280x1024 at 60-Hz refresh rate

- Serial ports

- One RS-232 port (Without DB-9 serial connector)

- One PS/2 port (Can be used through a PS/2 Y Cable to allow you to connect a keyboard and mouse to one port)

- Two 40-pin expansion headers

- 72 Cyclone III 3.3V I/O pins, as well as 8 power and ground lines, are brought out to two 40-pin expansion connectors

- 40-pin header is designed to accept a standard 40-pin ribbon cable used for IDE hard drives.

- Built-in USB Blaster circuit

- Home

- FPGA HARDWARE

- INTEL FPGA

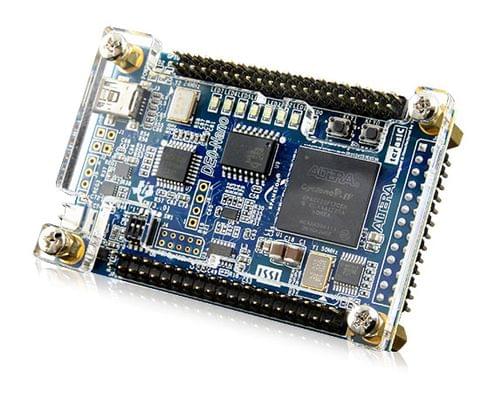

- Altera DE0 Board

Altera DE0 Board

SIZE GUIDE

- Shipping in 10-12 Working days

- http://cdn.storehippo.com/s/59c9e4669bd3e7c70c5f5e6c/ms.products/5b939c9eac9e63b27856cdcd/images/5b939c9eac9e63b27856cdce/5b939c4c5aed48b203b16972/5b939c4c5aed48b203b16972.jpg

Description of product

Description

The DE0 Development and Education board is designed in a compact size with all the essential tools for novice users to gain knowledge in areas of digital logic, computer organization and FPGAs. It is equipped with Altera Cyclone III 3C16 FPGA device, which offers 15,408 LEDs. The board provides 346 user I/O pins, and is loaded with a rich set of features that makes it suitable to be used for advanced university and college courses, as well as the development of sophisticated digital systems. The DE0 combines the Altera low-power, low-cost, and high performance Cyclone III FPGA to control the various features of the DE0 Board. The DE0 Development Board includes software, reference designs, and accessories required to ensure the user simple access in evaluating their DE0 Board.

- FPGA

- Cyclone III 3C16 FPGA

- 15,408 LEs

- 56 M9K Embedded Memory Blocks

- 504K total RAM bits

- 56 embedded multipliers

- 4 PLLs

- 346 user I/O pins

- FineLine BGA 484-pin package

- Cyclone III 3C16 FPGA

- Memory

- SDRAM

- One 8-Mbyte Single Data Rate Synchronous Dynamic RAM memory chip

- Flash memory

- 4-Mbyte NOR Flash memory

- Support Byte (8-bits)/Word (16-bits) mode

- SD card socket

- Provides both SPI and SD 1-bit mode SD Card access

- SDRAM

- Interface

- Built-in USB Blaster circuit

- On-board USB Blaster for programming

- Using the Altera EPM240 CPLD

- Altera Serial Configuration device

- Altera EPCS4 serial EEPROM chip

- Pushbutton switches

- 3 pushbutton switches

- Slide switches

- 10 Slide switches

- General User Interfaces

- 10 Green color LEDs

- 4 seven-segment displays

- 16x2 LCD Interface (Not include LCD module)

- Clock inputs

- 50-MHz oscillator

- VGA output

- Uses a 4-bit resistor-network DAC

- With 15-pin high-density D-sub connector

- Supports up to 1280x1024 at 60-Hz refresh rate

- Serial ports

- One RS-232 port (Without DB-9 serial connector)

- One PS/2 port (Can be used through a PS/2 Y Cable to allow you to connect a keyboard and mouse to one port)

- Two 40-pin expansion headers

- 72 Cyclone III 3.3V I/O pins, as well as 8 power and ground lines, are brought out to two 40-pin expansion connectors

- 40-pin header is designed to accept a standard 40-pin ribbon cable used for IDE hard drives.

- Built-in USB Blaster circuit

NEWSLETTER

Subscribe to get Email Updates!

Thanks for subscribe.

Your response has been recorded.

INFORMATION

ACCOUNT

ADDRESS

Tenet Technetronics# 2514/U, 7th 'A' Main Road, Opp. to BBMP Swimming Pool, Hampinagar, Vijayanagar 2nd Stage.

Bangalore

Karnataka - 560104

IN

Tenet Technetronics focuses on “Simplifying Technology for Life” and has been striving to deliver the same from the day of its inception since 2007. Founded by young set of graduates with guidance from ardent professionals and academicians the company focuses on delivering high quality products to its customers at the right cost considering the support and lifelong engagement with customers. “We don’t believe in a sell and forget model “and concentrate and building relationships with customers that accelerates, enhances as well as provides excellence in their next exciting project.