-

TRANSDUCERS

- TRANSDUCERS

-

BASIC COMPONENTS DK

- BASIC COMPONENTS DK

-

MARKETPLACE

- MARKETPLACE

-

DEVELOPMENT BOARDS & KITS

- DEVELOPMENT BOARDS & KITS

-

CABLE ASSEMBLIES

- CABLE ASSEMBLIES

-

RF AND WIRELESS

- RF AND WIRELESS

-

BOXES ENCLOSURES RACKS

- BOXES ENCLOSURES RACKS

-

AUDIO PRODUCTS

- AUDIO PRODUCTS

-

ARTILA

- ARTILA

-

FANS-BLOWERS-THERMAL MANAGEMENT

- FANS-BLOWERS-THERMAL MANAGEMENT

-

WIRELESS MODULES

- WIRELESS MODULES

-

TERMINALS

- TERMINALS

-

Cables/Wires

- Cables/Wires

-

SINGLE BOARD COMPUTER

- SINGLE BOARD COMPUTER

-

BREAKOUT BOARDS

- BREAKOUT BOARDS

-

LED

- LED

-

TEST AND MEASUREMENT

- TEST AND MEASUREMENT

-

POTENTIONMETERS AND VARIABLE RESISTORS

- POTENTIONMETERS AND VARIABLE RESISTORS

-

DEVELOPMENT BOARDS AND IC's

- DEVELOPMENT BOARDS AND IC's

-

EMBEDDED COMPUTERS

- EMBEDDED COMPUTERS

-

OPTOELECTRONICS

- OPTOELECTRONICS

-

INDUSTRAL AUTOMATION AND CONTROL

- INDUSTRAL AUTOMATION AND CONTROL

-

COMPUTER EQUIPMENT

- COMPUTER EQUIPMENT

-

CONNECTORS & INTERCONNECTS

- CONNECTORS & INTERCONNECTS

-

MAKER/DIY EDUCATIONAL

- MAKER/DIY EDUCATIONAL

-

TOOLS

- TOOLS

-

MOTORS/ACTUATORS/SOLEENOIDS/DRIVERS

- MOTORS/ACTUATORS/SOLEENOIDS/DRIVERS

-

FPGA HARDWARE

- FPGA HARDWARE

-

POWER SUPPLIES

- POWER SUPPLIES

-

ROBOTICS & AUTOMATION

- ROBOTICS & AUTOMATION

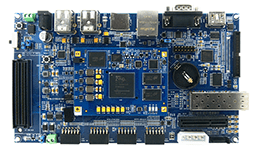

The MYD-C7Z015 development board is a programmable, low-cost and high-performance board designed by MYIR. It integrates Xilinx XC7Z015 (Z-7015) Dual-core ARM Cortex-A9 Processor with Xilinx 7-series FPGA logic from Xilinx Zynq-7000 family, with one PCIe interface and one SFP transceiver module interface on the base board to allow users to expand numerous of high-speed devices. It’s typically applications ranges from Industrial Automation, Test & measurement, Medical Equipment, Aerospace to military and more others.

The MYD-C7Z015 development board is using the MYC-C7Z015 CPU Module as the core controller board which integrates the core components including the Zynq-7015 processor, 1GB DDR3 SDRAM, 4GB eMMC, 32MB quad SPI Flash, a Gigabit Ethernet PHY, a USB PHY and external watchdog. The MYC-C7Z015 CPU Module is mounted on to the MYD-C7Z015 base board through two 0.8mm pitch 140-pin Board-to-Board connectors. Compared with the Zynq-7010, the processor Zynq-7015, has more logic cells, Block RAM and DSP slices, which makes the board obtain more powerful programmable function for users.

MYC-C7Z015 CPU Module as Controller Board

- Two 0.8mm pitch 140-pin Connectors for Board-to-Board Connections

- 766MHz Xilinx XC7Z015 Dual-core ARM Cortex-A9 Processor with Xilinx 7-series FPGA logic

- 1GB DDR3 SDRAM, 4GB eMMC, 32MB QSPI Flash

- Serial port, 4 x USB Host, Gigabit Ethernet, CAN, HDMI, LCD, TF

- 1 x XADC, 3 x PMoD, 1 x FMC, 1 x SFP Module, 1 x PCIe

- Optional 4.3 or 7 inch LCD/TSP

- Ready-to-Run Linux 3.15.0

- Home

- DEVELOPMENT BOARDS AND IC's

- MYD-C7Z015 Development Board

MYD-C7Z015 Development Board

SIZE GUIDE

- Shipping in 10-12 Working days

- http://cdn.storehippo.com/s/59c9e4669bd3e7c70c5f5e6c/ms.products/5b98e6a26321e4b750b12cc8/images/5b98e6a26321e4b750b12cc9/5b98e677446314b7cc60fddd/5b98e677446314b7cc60fddd.png

Description of product

The MYD-C7Z015 development board is a programmable, low-cost and high-performance board designed by MYIR. It integrates Xilinx XC7Z015 (Z-7015) Dual-core ARM Cortex-A9 Processor with Xilinx 7-series FPGA logic from Xilinx Zynq-7000 family, with one PCIe interface and one SFP transceiver module interface on the base board to allow users to expand numerous of high-speed devices. It’s typically applications ranges from Industrial Automation, Test & measurement, Medical Equipment, Aerospace to military and more others.

The MYD-C7Z015 development board is using the MYC-C7Z015 CPU Module as the core controller board which integrates the core components including the Zynq-7015 processor, 1GB DDR3 SDRAM, 4GB eMMC, 32MB quad SPI Flash, a Gigabit Ethernet PHY, a USB PHY and external watchdog. The MYC-C7Z015 CPU Module is mounted on to the MYD-C7Z015 base board through two 0.8mm pitch 140-pin Board-to-Board connectors. Compared with the Zynq-7010, the processor Zynq-7015, has more logic cells, Block RAM and DSP slices, which makes the board obtain more powerful programmable function for users.

MYC-C7Z015 CPU Module as Controller Board

- Two 0.8mm pitch 140-pin Connectors for Board-to-Board Connections

- 766MHz Xilinx XC7Z015 Dual-core ARM Cortex-A9 Processor with Xilinx 7-series FPGA logic

- 1GB DDR3 SDRAM, 4GB eMMC, 32MB QSPI Flash

- Serial port, 4 x USB Host, Gigabit Ethernet, CAN, HDMI, LCD, TF

- 1 x XADC, 3 x PMoD, 1 x FMC, 1 x SFP Module, 1 x PCIe

- Optional 4.3 or 7 inch LCD/TSP

- Ready-to-Run Linux 3.15.0

NEWSLETTER

Subscribe to get Email Updates!

Thanks for subscribe.

Your response has been recorded.

INFORMATION

ACCOUNT

ADDRESS

Tenet Technetronics# 2514/U, 7th 'A' Main Road, Opp. to BBMP Swimming Pool, Hampinagar, Vijayanagar 2nd Stage.

Bangalore

Karnataka - 560104

IN

Tenet Technetronics focuses on “Simplifying Technology for Life” and has been striving to deliver the same from the day of its inception since 2007. Founded by young set of graduates with guidance from ardent professionals and academicians the company focuses on delivering high quality products to its customers at the right cost considering the support and lifelong engagement with customers. “We don’t believe in a sell and forget model “and concentrate and building relationships with customers that accelerates, enhances as well as provides excellence in their next exciting project.