- TRANSDUCERS

- TRANSDUCERS

- BASIC COMPONENTS DK

- BASIC COMPONENTS DK

- MARKETPLACE

- MARKETPLACE

- DEVELOPMENT BOARDS & KITS

- DEVELOPMENT BOARDS & KITS

- CABLE ASSEMBLIES

- CABLE ASSEMBLIES

- RF AND WIRELESS

- RF AND WIRELESS

- BOXES ENCLOSURES RACKS

- BOXES ENCLOSURES RACKS

- AUDIO PRODUCTS

- AUDIO PRODUCTS

- FANS-BLOWERS-THERMAL MANAGEMENT

- FANS-BLOWERS-THERMAL MANAGEMENT

- WIRELESS MODULES

- WIRELESS MODULES

- TERMINALS

- TERMINALS

- Cables/Wires

- Cables/Wires

- SINGLE BOARD COMPUTER

- SINGLE BOARD COMPUTER

- BREAKOUT BOARDS

- BREAKOUT BOARDS

- LED

- LED

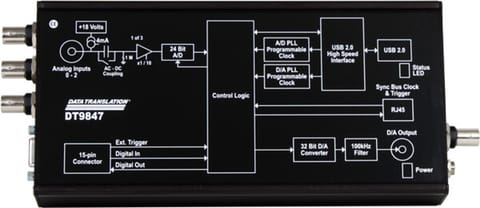

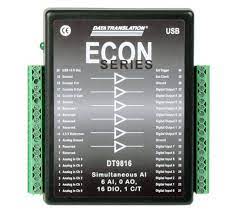

- TEST AND MEASUREMENT

- TEST AND MEASUREMENT

- POTENTIONMETERS AND VARIABLE RESISTORS

- POTENTIONMETERS AND VARIABLE RESISTORS

- DEVELOPMENT BOARDS AND IC's

- DEVELOPMENT BOARDS AND IC's

- EMBEDDED COMPUTERS

- EMBEDDED COMPUTERS

- OPTOELECTRONICS

- OPTOELECTRONICS

- INDUSTRAL AUTOMATION AND CONTROL

- INDUSTRAL AUTOMATION AND CONTROL

- COMPUTER EQUIPMENT

- COMPUTER EQUIPMENT

- CONNECTORS & INTERCONNECTS

- CONNECTORS & INTERCONNECTS

- MAKER/DIY EDUCATIONAL

- MAKER/DIY EDUCATIONAL

- TOOLS

- TOOLS

- MOTORS/ACTUATORS/SOLEENOIDS/DRIVERS

- MOTORS/ACTUATORS/SOLEENOIDS/DRIVERS

- FPGA HARDWARE

- FPGA HARDWARE

- ROBOTICS & AUTOMATION

- ROBOTICS & AUTOMATION

The joint test action group (JTAG) HS2 programming cable is a high-speed programming solution for Xilinx® field-programmable gate arrays (FPGAs). The cable is fully compatible with all Xilinx tools and can be seamlessly driven from iMPACT™, ChipScope™, and EDK. The HS2 attaches to target boards using Digilent's 6-pin, 100-mil spaced programming header or Xilinx's 2x7, 2mm connector and the included adaptor.

The PC powers the JTAG-HS2 through the USB port and will recognize it as a Digilent programming cable when connected to a PC, even if the cable is not attached to the target board. The HS2 has a separate Vdd pin to supply the JTAG signal buffers. The high-speed 24mA three-state buffers allow target boards to drive the HS2 with signal voltages from 1.8V to 5V and bus speeds of up to 30MBit/sec. To function correctly, the HS2's Vdd pin must be tied to the same voltage supply that drives the JTAG port on the FPGA.

The JTAG bus can be shared with other devices as systems hold JTAG signals at high-impedance except when actively driven during programming. The HS2 comes included with a standard Type-A to Micro-USB cable that attaches to the end of the module opposite the system board connector. The system board connector should hold the small and light HS2 firmly in place.

Note: This cable is not needed for Digilent FPGA boards as our boards are designed with this functionality natively.

- Analog Devices ADP123AUJZ Linear Regulator

- Small, complete, all-in-one JTAG programming solution for Xilinx FPGAs

- Compatible with all Xilinx tools

- Compatible with IEEE 1149.7-2009 Class T0 - Class T4 (includes 2-Wire JTAG)

- Separate Vref drives JTAG/SPI signal voltages; Vref can be any voltage between 1.8V and 5V.

- High-Speed USB2 port that can drive JTAG/SPI bus at up to 30Mbit/sec

- JTAG/SPI frequency settable by user

- Uses micro-AB USB2 connector

- SPI programming solution (modes 0 and 2 up to 30Mbit/sec, modes 1 and 3 up to 2Mbit/sec)

- Fully supported by Digilent's Adept software and Adept SDK, allowing custom JTAG/SPI applications to be created

- One JTAG-HS2 Program.ming Cable

JTAG-HS2 Programming Cable

SIZE GUIDE

- Shipping in 12-14 Working Days

Description of product

The joint test action group (JTAG) HS2 programming cable is a high-speed programming solution for Xilinx® field-programmable gate arrays (FPGAs). The cable is fully compatible with all Xilinx tools and can be seamlessly driven from iMPACT™, ChipScope™, and EDK. The HS2 attaches to target boards using Digilent's 6-pin, 100-mil spaced programming header or Xilinx's 2x7, 2mm connector and the included adaptor.

The PC powers the JTAG-HS2 through the USB port and will recognize it as a Digilent programming cable when connected to a PC, even if the cable is not attached to the target board. The HS2 has a separate Vdd pin to supply the JTAG signal buffers. The high-speed 24mA three-state buffers allow target boards to drive the HS2 with signal voltages from 1.8V to 5V and bus speeds of up to 30MBit/sec. To function correctly, the HS2's Vdd pin must be tied to the same voltage supply that drives the JTAG port on the FPGA.

The JTAG bus can be shared with other devices as systems hold JTAG signals at high-impedance except when actively driven during programming. The HS2 comes included with a standard Type-A to Micro-USB cable that attaches to the end of the module opposite the system board connector. The system board connector should hold the small and light HS2 firmly in place.

Note: This cable is not needed for Digilent FPGA boards as our boards are designed with this functionality natively.

- Analog Devices ADP123AUJZ Linear Regulator

- Small, complete, all-in-one JTAG programming solution for Xilinx FPGAs

- Compatible with all Xilinx tools

- Compatible with IEEE 1149.7-2009 Class T0 - Class T4 (includes 2-Wire JTAG)

- Separate Vref drives JTAG/SPI signal voltages; Vref can be any voltage between 1.8V and 5V.

- High-Speed USB2 port that can drive JTAG/SPI bus at up to 30Mbit/sec

- JTAG/SPI frequency settable by user

- Uses micro-AB USB2 connector

- SPI programming solution (modes 0 and 2 up to 30Mbit/sec, modes 1 and 3 up to 2Mbit/sec)

- Fully supported by Digilent's Adept software and Adept SDK, allowing custom JTAG/SPI applications to be created

- One JTAG-HS2 Program.ming Cable

NEWSLETTER

Subscribe to get Email Updates!

Thanks for subscribe.

Your response has been recorded.

INFORMATION

ACCOUNT

ADDRESS

Tenet Technetronics# 2514/U, 7th 'A' Main Road, Opp. to BBMP Swimming Pool, Hampinagar, Vijayanagar 2nd Stage.

Bangalore

Karnataka - 560104

IN

Tenet Technetronics focuses on “Simplifying Technology for Life” and has been striving to deliver the same from the day of its inception since 2007. Founded by young set of graduates with guidance from ardent professionals and academicians the company focuses on delivering high quality products to its customers at the right cost considering the support and lifelong engagement with customers. “We don’t believe in a sell and forget model “and concentrate and building relationships with customers that accelerates, enhances as well as provides excellence in their next exciting project.